|

软件简介:上一页dxwebsetup离线安装包 V9.0 官方最新免费非破解版下载 下一页sciex os(高分辨质谱软件) V2.0.1 官方最新免费非破解版下载

本软件是由七道奇为您精心收集,来源于网络转载,软件收录的是官方版,软件版权归软件作者所有,本站不对其观点以及内容做任何评价,请读者自行判断,以下是其具体内容: maxplus2是一款功能强大的PLD开发软件,能够帮助用户更好的进行FPGA/CPLD的开发工作,用户可以使用软件完成设计输入、元件适配、时序仿真、功能仿真等流程,提高工作效率。软件已经成功破解,内置了完美破解补丁,可以免费解锁全部功能。

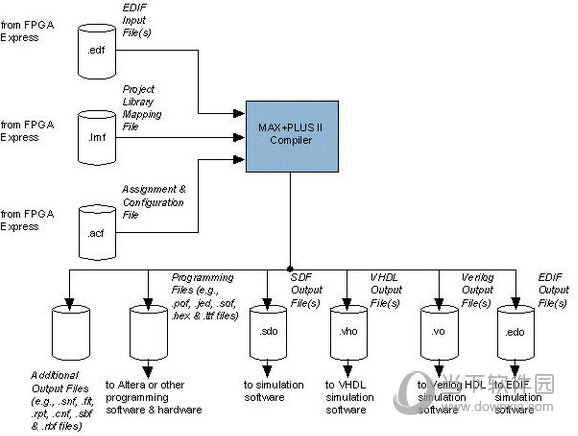

【软件功能】1、设计输入,在传统设计中,设计人员是应用传统的原理图输入方法来开始设计的。自90年代初, Verilog、VHDL、AHDL等硬件描述语言的输入方法在大规模设计中得到了广泛应用。 2、前仿真(功能仿真),设计的电路必须在布局布线前验证电路功能是否有效。(ASCI设计中,这一步骤称为第一次Sign-off)PLD设计中,有时跳过这一步。 3、设计编译,设计输入之后就有一个从高层次系统行为设计向门级逻辑电路设转化翻译过程,即把设计输入的某种或某几种数据格式(网表)转化为软件可识别的某种数据格式(网表)。 4、优化,对于上述综合生成的网表,根据布尔方程功能等效的原则,用更小更快的综合结果代替一些复杂的单元,并与指定的库映射生成新的网表,这是减小电路规模的一条必由之路。 5、布局布线,在PLD设计中,3-5步可以用PLD厂家提供的开发软件(如 Maxplus2)自动一次完成。 6.后仿真(时序仿真)需要利用在布局布线中获得的精确参数再次验证电路的时序。(ASCI设计中,这一步骤称为第二次Sign—off)。 7、生产,布线和后仿真完成之后,就可以开始ASCI或PLD芯片的投产

【软件特色】1、开放的界面,支持与Cadence,Exemplarlogic,Mentor Graphics,Synplicty,Viewlogic和其它公司所提供的EDA工具接口。 2、与结构无关,系统的核心Complier支持Altera公司的FLEX10K、FLEX8000、FLEX6000、MAX9000、MAX7000、MAX5000和Classic可编程逻辑器件,提供了世界上唯一真正与结构无关的可编程逻辑设计环境。 3、完全集成化,设计输入、处理与较验功能全部集成在统一的开发环境下,这样可以加快动态调试、缩短开发周期。 4、丰富的设计库,提供丰富的库单元供设计者调用,其中包括74系列的全部器件和多种特殊的逻辑功能(Macro-Function)以及新型的参数化的兆功能(Mage-Function)。 5、模块化工具,设计人员可以从各种设计输入、处理和较验选项中进行选择从而使设计环境用户化。 6、硬件描述语言(HDL),软件支持各种HDL设计输入选项,包括VHDL、Verilog HDL和Altera自己的硬件描述语言AHDL。 7、Opencore特征,软件具有开放核的特点,允许设计人员添加自己认为有价值的宏函数。

【破解说明】1、运行"PCALTERA32BIT"目录下的"SETUP.EXE", 点击Install SoftwareMAX+PLUS II BASELINE Software安装软件。 2、第一次运行MAX+plus II时,会弹出一个"遵守协议"对话框, 用鼠标将内容下拉到最后, 选择“OK“。 3、将安装盘目录下的授权文件,复制到MAX+plus II的安装目录下(如"C:MAXPLUS2"目录)。 4、再次启动MAX+plus II,选择菜单[Option]->[Setup]功能, 在弹出的对话框中,按"Browse"按钮,选择刚才复制的授权文件, 确认退出,退出MAX+plus II开发环境,再次运行MAX+plus II即可。 【下载地址】max plus ii破解版 V10.2 免费版“max plus ii破解版 V10.2 免费非破解版下载[绿色软件]”系转载自网络,如有侵犯,请联系我们立即删除,另:本文仅代表作者个人观点,与本网站无关。其原创性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容、文字的真实性、完整性、及时性七道奇不作任何保证或承诺,请读者仅作参考,并请自行核实相关内容。 |

|||||||||||||||||||||||